TileCal Electronics for HL-LHC

ATLAS Upgrades for Enhanced Performance at the Large Hadron Collider

The Large Hadron Collider (LHC) has played a crucial role in advancing our understanding

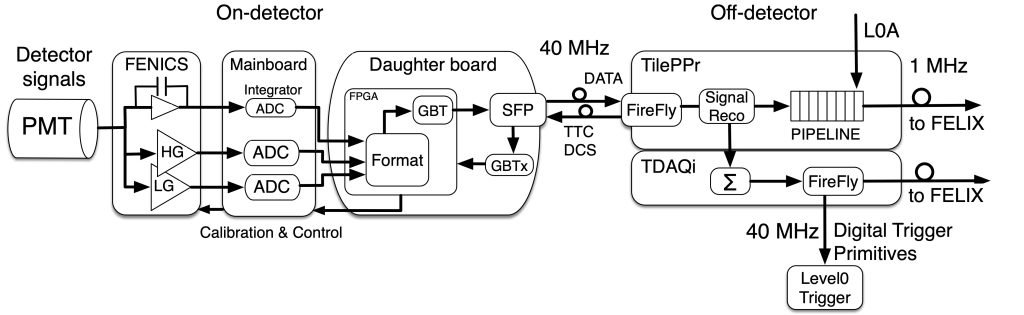

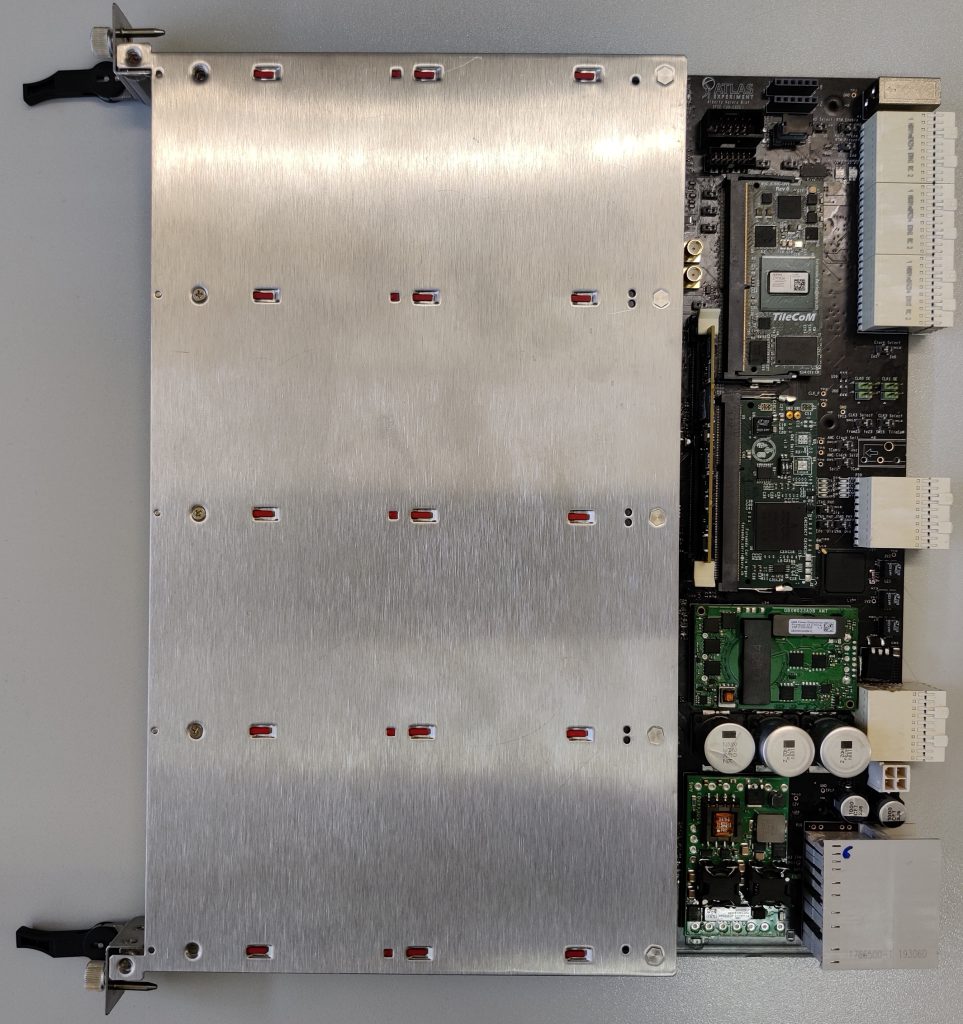

of fundamental physics since 2009. To maintain and expand the LHC’s discovery potential, the High-Luminosity LHC (HL-LHC) project is planned as a major upgrade. As part of this upgrade, the ATLAS experiment has developed a comprehensive roadmap for upgrades, including the installation of new detector components and advancements in data acquisition and processing systems. A crucial component of these enhancements involves the complete replacement of the ATLAS central Tile hadronic calorimeter readout electronics. This upgrade aims to optimize the system’s ability to handle higher data rates and improve its resilience to radiation. Through these comprehensive improvements, the ATLAS experiment aims to meet the requirements and seize the opportunities presented by the HL-LHC era. Our group is responsible for the design, production and installation of the TilePPr (Tile PreProcessor) module, which serves as a crucial interface between the on-detector electronics and the central systems of the ATLAS experiment, including Data Acquisition, Detector Control, and Trigger systems. The TilePPr module is based on theAdvanced Telecommunications Computing Architecture (ATCA) and incorporates high-speed optical links, communication interfaces, and data processing capabilities.

The TileCal Preprocessor

To cope with the increased number of interactions expected at the HL-LHC, the ATLAS detector has redesigned the Trigger and DAQ system. The new architecture is based on a fully digital Level-0 trigger: with a maximum latency of 10 s and an average rate of 1 MHz which is ten times higher than the present first level of trigger.

The photomultiplier signals are amplified and digitized with two 12-bit ADCs in the Mainboard at 40.08 MHz, synchronously with the HL-LHC bunch crossing. The digital samples are gathered by the Daughterboard which transfers the data continuously through high-speed optical links to the TileCal PreProcessor (TilePPr) located off-detector. The TilePPr stores the high and low gain digital samples into pipeline FIFO memories. In parallel, the deposited cell energy is estimated for every bunch crossing and transmitted to the Trigger and DAQ interface (TDAQi) module. The TDAQi module builds trigger primitive objects which are transferred into the Level-0 trigger system. Upon the reception of a Level-0 acceptance signal, the selected data events are transferred to the Front End LInk eXchange (FELIX) system which implements the interface with the central ATLAS DAQ system. Moreover, the TilePPr receives and propagates to the on-detector electronics the HL-LHC synchronous clock and configuration commands. It also provides a low bandwidth data path for monitoring and control purposes.